TI AM6231 上电时序要求

TI AM6231 是一款高性能的嵌入式处理器,广泛应用于工业控制、通信和消费电子等领域。为了确保 AM6231 能够稳定、可靠地启动,合理的上电时序设计至关重要。本文将介绍 AM6231 的上电时序要求,帮助设计人员在进行硬件设计时确保电源系统的可靠性。

1. 上电时序的重要性

上电时序指的是在系统启动过程中,各个电源轨的上电顺序、上电延迟和稳定性要求。正确的上电时序可以确保 AM6231 处理器及其外围电路正常初始化,避免出现硬件损坏或系统异常启动的情况。AM6231 处理器的上电时序要求不仅涉及电源轨的启动顺序,还包括不同电源之间的延时和时序控制。

2. AM6231 上电时序要求

AM6231 的上电时序主要包括以下几个方面:

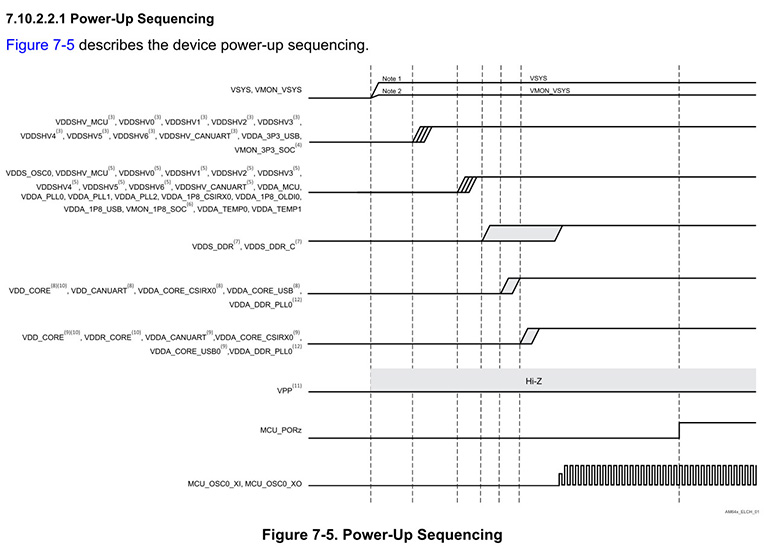

图一 AM62的上电时序要求

2.1 I/O 电源(VDDSHVx [x=0-6])

电压输出:I/O 电源由 LDO 稳压器提供,典型电压为 3.3V 或 1.8V,根据应用需求而定。

2.2 内存电源(VDDS_DDR)

电压输出:内存电源由 DCDC 转换器提供,给内存供电。

2.3 核心电源(VDD_CORE)

电压输出:核心电源通常由 DCDC 转换器提供

稳定性要求:VDD_CORE 电压稳定性至关重要。应确保在上电过程中电压波动不超过 10%,以防止处理器无法正常启动。

稳定性要求:关系到内存的工作稳定,至关重要。

AM62x系列和其他处理器的区别是,这三个主要电源的上电顺序是,VDDSHVx à VDDS_DDR à VDD_CORE,也就是IO供电先上,然后在DDR供电,然后再试CORE电压。其他的很多处理器是CORE先上电,所以这里需要注意的。

3. 上电时序中其他电源介绍

3.1. VSYS 表示为整个系统供电的电源的名称。该电源应为预调节电源,为电源管理设备供电,而电源管理设备又为所有其他电源供电。

3.2. VMON_VSYS 输入用于通过外部电阻分压器电路监控 VSYS。有关更多信息,请参阅系统电源监控器设计指南。

3.3. VDDSHV_CANUART、VDDSHV_MCU 和 VDDSHVx [x=0-6] 是双电压 IO 电源,可根据应用要求在 1.8V 或 3.3V 下运行。使用部分 IO 低功耗模式时,应将 VDDSHV_CANUART 连接到常开电源,不使用部分 IO 低功耗模式时,应连接到任何有效的 IO 电源。当 VDDSHV_CANUART 未连接到常开电源并以 3.3V 运行时,应在此波形定义的 3.3V 上升期内与其他 3.3V 电源一起上升。当任何 VDDSHV_MCU 和 VDDSHVx [x=0-6] IO 电源以 3.3V 工作时,它们应在该波形定义的 3.3V 斜坡期间与其他 3.3V 电源一起上升。

3.4. VMON_3P3_SOC 输入用于监控电源电压,并应连接到相应的 3.3V 电源。

3.5. VDDSHV_CANUART、VDDSHV_MCU 和 VDDSHVx [x=0-6] 是双电压 IO 电源,可根据应用要求在 1.8V 或 3.3V 下工作。使用部分 IO 低功耗模式时,VDDSHV_CANUART 应连接到始终开启的电源,不使用部分 IO 低功耗模式时,应连接到任何有效的 IO 电源。当 VDDSHV_CANUART 未连接到常开电源并以 1.8V 运行,则应在此波形定义的 1.8V 斜坡期间,使用其他 1.8V 电源对其进行斜坡上升。当任何 VDDSHV_MCU 和 VDDSHVx [x=0-6] IO 电源以 1.8V 运行,则应在此波形定义的 1.8V 斜坡期间,使用其他 1.8V 电源对其进行斜坡上升。

3.6. VMON_1P8_SOC 输入用于监控电源电压,并应连接到相应的 1.8V 电源。

3.7. VDDS_DDR 和 VDDS_DDR_C 应由同一电源供电,以便它们一起斜坡上升。

3.8. 使用部分 IO 低功耗模式时,应将 VDD_CANUART 连接到常开电源;不使用部分 IO 低功耗模式时,应将 VDD_CANUART 连接到与 VDD_CORE 相同的电源。 VDD_CORE、VDDA_CORE_CSIRX0、VDDA_CORE_USB 和 VDDA_DDR_PLL0 应始终来自同一电源,并且可以在 0.75V 或 0.85V 下工作。当这些电源在 0.75V 下工作时,它们应先于所有 0.85V 电源上升,如该波形所示。

3.9. 使用部分 IO 低功耗模式时,VDD_CANUART 应连接到始终开启的电源,或不使用部分 IO 低功耗模式时连接到与 VDD_CORE 相同的电源。VDD_CORE、VDDA_CORE_CSIRX0、VDDA_CORE_USB 和 VDDA_DDR_PLL0 应来自同一电源,并且可以在 0.75V 或 0.85V 下工作。当这些电源以 0.85V 工作时,它们应在该波形定义的 0.85V 斜坡周期内与其他 0.85V 电源一起上升。

3.10. 加电或断电期间施加到 VDDR_CORE 的电位绝不能大于施加到 VDD_CORE + 0.18V 的电位。这要求当 VDD_CORE 以 0.75V 工作时,VDD_CORE 在 VDDR_CORE 之前上升并在 VDDR_CORE 之后下降。除了为 VDDR_CORE 定义的斜坡要求外,VDD_CORE 没有其他斜坡要求。VDD_CORE 和 VDDR_CORE 应由同一电源供电,因此当 VDD_CORE 以 0.85V 工作时,它们一起上升。

3.11. VPP 是 1.8V eFuse 编程电源,在加电/断电序列和正常设备操作期间应保持浮动(HiZ)或接地。仅在编程 eFuse 时才应使用此电源。

3.12. VDDA_DDR_PLL0 连接到 ALW 封装内的 VDD_CORE。

4. 总结

TI AM6231 的上电时序设计对于确保系统的稳定性和可靠性至关重要。通过合理的电源时序设计、延时控制和信号保护,开发人员可以有效防止因电源问题导致的系统启动失败或异常行为。设计时应特别关注各个电源轨之间的依赖关系,并确保每个电源在合适的时间点稳定启动,以确保 AM6231 处理器及其外设正常工作。

维芯科作为TI的第三方合作伙伴,在电路设计方面可以提供一定的支持,推荐使用维芯科设计的AM62x核心板

WTC-AM62XXS核心板: https://www.weathink.cn/products/hexinban/11.html